-

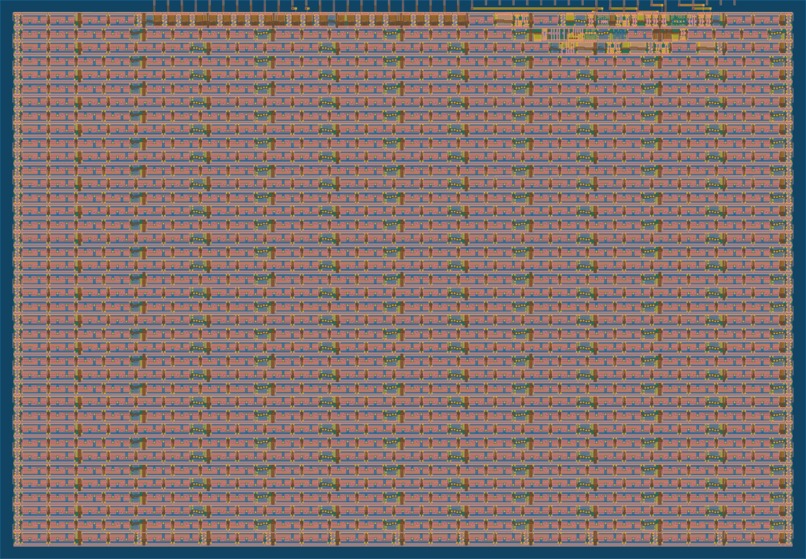

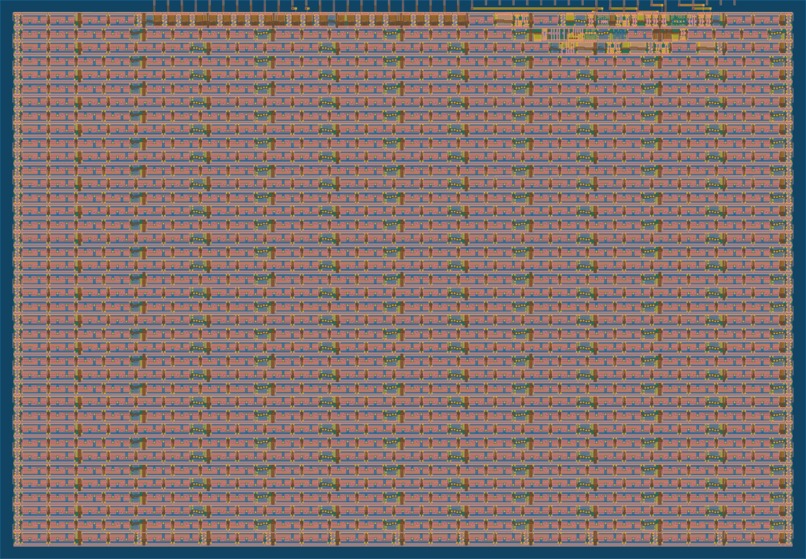

The complete silicon blueprint of Neuro-Kinematic. Our PyTorch model physically hardcoded into custom logic gates for zero-latency AI.

-

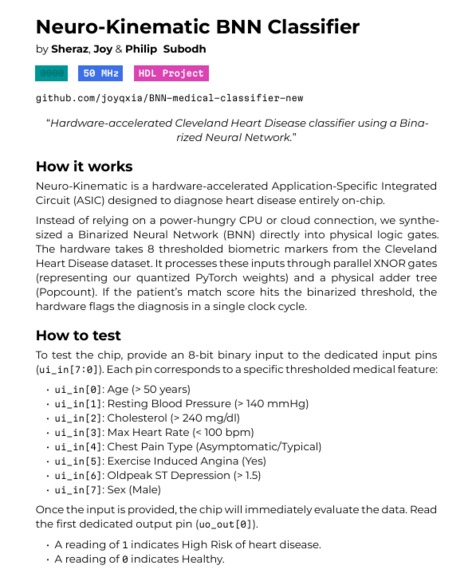

Official hardware datasheet and pin-out configuration for the Neuro-Kinematic ASIC.

-

A fully green CI/CD pipeline! Our design passed all foundry prechecks and gate-level physical simulations.

Inspiration

Current medical wearables are power-hungry. They constantly transmit raw, sensitive patient vitals to cloud servers or rely on heavy onboard CPUs to run machine learning models. This drains batteries and creates massive data privacy risks. We wanted to see if we could completely eliminate the software layer. Our goal was to build a medical diagnostic AI that exists purely as a physical entity; A chip that diagnoses heart disease instantaneously, securely, and using only micro-watts of power.

What it does

Neuro-Kinematic is a custom Application-Specific Integrated Circuit (ASIC). Instead of running a neural network in software, we built the network into the silicon itself. The chip takes 8 thresholded biometric markers (like Age, Blood Pressure, and Cholesterol) as physical electrical inputs. It pushes those signals through parallel XNOR logic gates and a hardware adder tree (Popcount). If the patient’s vitals match the embedded binarized weights, the chip flags a "High Risk" diagnosis in a single clock cycle (under 20 nanoseconds).

How we built it

Statistical Thresholding: Bringing AI to the physical layer requires extreme optimization. Applying rigorous statistical methods, we analyzed the Cleveland Heart Disease dataset to extract the 8 most critical biometric markers, perfectly mapping our data strictly to our 8-pin hardware limitation.

Hardware-Aware AI Training: Standard AI models use floating-point numbers, which require massive silicon real estate to compute. We wrote a custom PyTorch model using a Straight-Through Estimator to force the network to learn using strictly binary weights (0 or 1).

Silicon Synthesis: We translated those trained binary weights into Verilog. We replaced complex mathematical multipliers with simple, microscopic XNOR gates.

Physical Verification: We used Tiny Tapeout and GitHub Actions to route the physical GDSII layout. Using cocotb, we fed real patient data into the simulated transistors to verify the logic.

Challenges we ran into

The Propagation Delay: In software, math happens instantly. In hardware, electrons take time to travel. Our automated testbench kept failing because it was trying to read the diagnosis before the electricity had physically traveled through the input synchronizers. We had to rewrite our test script to account for a 5-clock-cycle propagation delay.

The Power Supply Phantom Bug: During gate-level simulation, our chip kept outputting an "Unknown" state. We realized we had accidentally bypassed the virtual power wrapper (tb.v) in our Makefile. Our microscopic logic gates literally had no electricity!

Quantization Sensitivity: Squashing complex data into a 1-bit model caused our hardware to initially misclassify a high-risk patient. We had to carefully recalculate and adjust the hardware thresholding logic from 5 down to 4 matches to restore perfect diagnostic sensitivity.

Accomplishments that we're proud of

100% Hardware-to-Software Parity: Our physical logic gates triggered the exact same disease risk flag as our PyTorch model on our test data.

A "Perfect Build": We achieved a fully green CI/CD pipeline, passing DRC (Design Rule Checks), Prechecks, and Gate-Level tests. The chip is officially manufacturable.

Full-Stack Teamwork: We successfully merged data science, machine learning, and low-level Verilog engineering in a single 8-hour sprint.

What we learned

We learned that the cloud makes you lazy! When you only have a few dozen physical logic gates to work with, every single bit of data matters. We learned how to manipulate a PyTorch loss function to understand physical hardware constraints, and how to debug digital logic down to the nanosecond.

What's next for Neuro-Kinematic: AI Hardcoded in Silicon

Our next step is physical deployment. Because this ASIC draws almost zero power, it is the perfect candidate for a kinetic-powered wearable (powered purely by the user's body movement). We also plan to implement an SRAM-based weight registry, allowing doctors to securely flash updated AI models to the hardware without altering the physical logic gates.

Built With

- asic

- cocotb

- github-actions

- hardware-design

- machine-learning

- pandas

- python

- pytorch

- tinytapeout

- verilog

Log in or sign up for Devpost to join the conversation.